Our Best Offer Ever!! Summer Special - Get 3 Courses at 24,999/- Only. Read More

Our Best Offer Ever!! Summer Special - Get 3 Courses at 24,999/- Only. Read More

VLSI Training In Chennai

- Real Time Experts as Trainers

- Certification

- Flexibility

- LIVE Project

- Affordable Fees

- Placement Support

Have Queries? Talk to our Career Counselor for more Guidance on picking the right career for you!

About VLSI Training

Over the past several years, Silicon CMOS innovation has turned into the predominant creation prepare for generally superior and savvy VLSI circuits. The progressive way of these advancements is comprehended by the quick development in which the number of transistors coordinated on circuits on a single chip. In this instructional exercise, we are giving an idea of MOS coordinated circuits and coding of VHDL and Verilog dialect. Prior to the presentation of VLSI innovation, most ICs had a constrained arrangement of capacities they could perform. An electronic circuit may comprise a CPU, ROM, RAM, and another paste rationale. VLSI gives IC fashioners a chance to include these into one chip.

VLSI Courses at DLK

Very-large-scale integration (VLSI) is the way toward making a coordinated circuit (IC) by joining a large number of transistors into a solitary chip. VLSI started in the 1970s when complex semiconductor and correspondence advances were being created. The chip is a VLSI gadget. The gadgets business has accomplished a remarkable development in the course of the most recent couple of decades, principally because of the quick advances in vast scale mix advances and framework plan applications. With the appearance of expansive scale incorporation (VLSI) plans, the quantity of uses of coordinated circuits (ICs) in superior registering, controls, media communications, picture, and video handling, and shopper gadgets has been ascending at a quick pace. Vlsi Training Institute in Chennai The present bleeding edge advances, for example, high determination and low piece rate video and cell interchanges give the end-clients a grand measure of utilizations, preparing force and transportability. This pattern is relied upon to develop quickly, with vital ramifications on the VLSI plan and frameworks outline.

Course Highlights and Why VLSI in Chennai at DLK?

- Course Timing- All days Monday to Saturday from 10 am to 7 pm.

- Training hours – 48 to 60 hours

- Course – Training in Software installation

- Hardware – We make hardware, and show how is it working.

- Course Documentation, with PPT or PDF, and project report.

- Certificate – After Successful completion of the training, certification will be done by us.

Online Training

Instructor

LED Live

Online Training

Classroom Training

Instructor

LED Classroom

Training

One to One Training

Customized and Exclusive training based on your requirement.

Team/Corporate Training

Customized Corporate Training

Syllabus

- FPGA Vs ASIC

- Advanced Design

- CMOS

- VHDL

- Binary arithmetic, Boolean algebra, Logic Gates, Combinational circuits, sequential circuits

- Advanced digital design, processor design, Data path & control unit design

- State machine Design

- MOS Fundamentals and Characterization, NMOS/PMOS/CMOS Technologies

- Fabrication Principles, Different Styles of Fabrication for NMOS/PMOS/CMOS

- Design with CMOS Gates, Characterization of CMOS Circuits

- Subsystem Design, Layout Representation for CMOS Circuits, Design Exercise using CMOS

- Introduction of IC Design, Different Methodologies for IC Design

- Fabrication Flows and Fundamentals

- Levels of Abstraction, Entity, Architecture

- Data Types and declaration, Enumerated Data Types

- Relational, Logical, Arithmetic Operators

- Language introduction, Levels of abstraction, Module, Ports types, and declarations

- Registers and nets, Arrays, Identifiers, Parameters, Relational, Arithmetic, Logical, Bit-wise shift Operators

- Writing expressions, Behavioral Modeling, Procedural Statements

- Process Statement, Concurrent Statements, When-else, With-select

- If-then-else, Case, Slicing and Concatenation, Loop Statements

- Arrays, Memory Modeling, FSM, Writing Procedures, Behavioral / RTL Coding

- System Verilog Declaration spaces, System Verilog Literal Values, and Built-in Data Types

- System Verilog User-Defined and Enumerated Types, System Verilog Arrays, Structures, and Unions

- System Verilog Procedural Blocks, Tasks, and Function, System Verilog Procedural Statements

- Re-configurable Devices, FPGA’s/CPLD’s, Architectures of XILINX, ALTERA Devices, SDF Format

- Designing with FPGAs, FPGA’s and its Design Flows, Architecture based coding, DSP on FPGA

- Back annotation, gate level simulation, Hands on experience with industry Standard Tools

Have Queries? Talk to our Career Counselor for more Guidance on picking the right career for you!

[popup_anything id="4878"]

Trainer Profile

- Our trainers are well versed in technical wise and they are knowledgeable in their professions

- Our trainers will explain the students in a very easy method, such a way the students will understand easily.

- Our trainers will put their maximum effort in explaining the students

- Our trainers have well experienced and put their full effort in explaining during the discussion with the students

- Our trainers will give attention individually to all the student by one on one, until the student get well versed in it.r trainers have well experienced and put their full effort in explaining during the discussion with the students

Real-Time Experts as Trainers

The trainers are very professionals and friendly. Our trainers are passionate for training the students and well versed with concepts of modules and the students doubts will be also cleared in a good manner.

Live Project

We offer world class teaching and top-notch training to help you discover and groom the technical ability in you. We provide best-in-class infrastructure, online resources, and exposure to you in this world of IT.

Certification

When we Certify a Professional , he knows exactly how to deliver a successful project. So get certified, showcase your skills and share your knowledge. Earning certification helps you as an IT professional establish credibility with both your employer and the greater IT industry.

Affordable Fees

Our fees is very normal and affordable to all the students in all their criteria.

Flexibility

Our Training classes offers flexible training options including Class room and online /off line training for your learning needs. Choose what to learn, and when and how to learn it. With our trainers or accredited instructors in a hands-on learning environment.

Placement Support

In placement, we support you in all the ways by giving you well training in your prescribed domain in which will you be able to handle by your own and well versed.

VLSI Certification Training in Chennai

[popup_anything id="4878"]

Course Training Meterial

- We take one to one responsibility to every student

- Study Materials will be given

- Programming code – issued

- Hardware – We Guidelines in Technology – will be explained well.make hardware, and show how is it working.

Course Certificate

- After completion of the training, successfully, the student will be issued a course completion certificate.

Who Can Attend this Programme?

- College students from 1st year to 4th year

- Fresh pass-out students

- Peoples who are searching good jobs

Outcome Of This Training Programme?

- Will be a well-trained Programmer before graduation

- Will be a well-trained Programmer before graduation

- Acceptance of work in all their fields

- To develop good attitude, speedy in their work

- Will get good placements in MNC’s

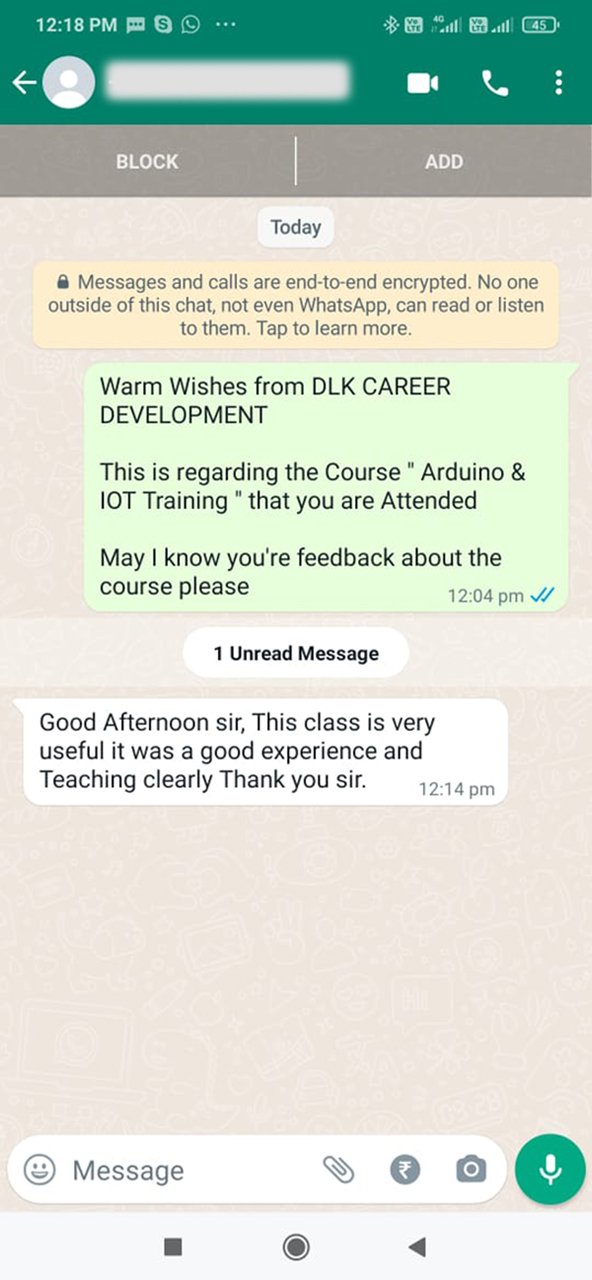

Students Reviews

Our Students Works At